Lecture

From the developer’s point of view, the situation on the network equipment market is characterized by three main trends: network traffic is constantly growing, requiring updating of the existing infrastructure; there are new technologies, services and standards that are relatively quickly implemented; There is a convergence of voice and data. All this in the conditions of tough competition dictates the acceleration of development rates, the need to quickly bring products to market and the availability of the possibility of simple modification of previously developed devices. These requirements are fulfilled if the majority of changes are made in software, and not in hardware. One approach to solving the problem is to create so-called network processors.

By definition, a network processor (network processor, NP) is a programmable processor whose architecture is optimized for use in network devices and providing robust packet processing.

If you look at the history of their appearance, it should be noted that initially, when computer networks were slow, the data packets transmitted through them were processed by conventional processors. And everything would be fine, but with the increase in network bandwidth, the performance of such processors began to be lacking. The next step (the beginning of the 1990s) was the widespread introduction of customized microchips (ASIC) into network equipment. In addition, general-purpose processors were used in conjunction with ASIC, but they processed a small percentage of packets related to network management, routing, and device configuration. However, network technologies quickly replace each other, while custom chips, although they can be configured, cannot be reprogrammed. They lack the flexibility of conventional processors, where all changes can be made at the software replacement level. Because of this, the development time in the life cycle of the upgraded network device turned out to be too long. Thus, the current network processors have combined both approaches: they have become programmable and specialized.

The current scheme is as follows: the network equipment is set by the CPU + network processor, which can be programmed to work with the specified network interfaces; in addition, they have a significantly higher speed due to the fact that the execution of many operations inside them is parallelized.

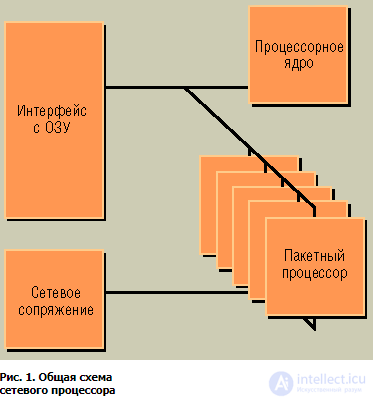

General scheme of the network processor

A network processor (see Fig. 1) consists of a processor core (there may be several in NP), executing programs, packet processing processors, and hardware accelerators that unload the CPU from routine functions, such as calculating checksums. In addition, it includes interface modules with RAM and high-speed bus interfaces. At the same time, the network processor is optimized for the task it performs, or, as they say, for network functionality.

Function 3 in the PP is implemented in software, the rest - in hardware. Since the batch processor architecture is optimized to perform common packet processing tasks (data copying, table scans, protocol conversion, etc.), they are designed either as mini-RISC processors or as DSP macrocell processors.

The shared RAM interface is used by both the kernel and batch processors.

Finally, the block of the high-speed physical layer interface (there may be several of them to support different types of networks) provides NP communication with the microcircuits connecting it to the network.

As an example, consider the structure of the Intel network processor IPX 1200 (Fig. 2). It is based on the StrongARM 32-bit RISC processor core, contains six packet mini-RISC processors (supports up to 256 MB of SDRAM RAM), as well as interfaces to the PCI system bus and the 64-bit IX bus that supports a set of ATM network interfaces, T1 / E1, 10, 100 and 1024 Mbit / s Ethernet, etc.

Each batch processor has a local control memory with a volume of 1 kslo and supports four threads, i.e., NP can simultaneously process up to 24 packets. The total bandwidth of this NP is 1.2 Gb / s, or 2.4 million packets / s.

In high-performance NPs, due to reliability and robustness requirements, real-time process-oriented systems such as OS-9 are usually used. A feature of the network processor OS (NPOS) is that it must be able, without stopping work (or with minimal downtime), to dynamically add, delete, or replace individual components of the system or application. This is important, for example, when changing the packet processing algorithm when a device is modified. A separate topic is the security of the OS network processors.

Comments

To leave a comment

History of computer technology and IT technology

Terms: History of computer technology and IT technology