Lecture

The elemental base of neural computing systems of the second and third directions (see part 1, part 2) are transputers, digital signal processors (DSP), FPGAs and neurochips, respectively. Moreover, the use of both those and others allows us to implement neural calculators that function in real time.

Element base of perspective neurocalculators are neurochips. Their production is carried out in many countries of the world, most of which are today focused on closed use (that is, they were created for specific specialized control systems). The main characteristics of commercially available neurochips are listed in Table 1 [1-8].

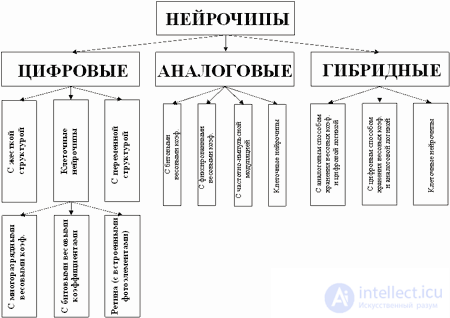

Before proceeding to the consideration of the most interesting neurochips, we will focus on their classification.

By the type of logic, they can be divided into digital, analog and hybrid.

By the type of implementation of neuroalgorithms: with fully hardware implementations and with software and hardware implementation (when neuroalgorithms are stored in ROM).

By the nature of the implementation of nonlinear transformations: on neurochips with a rigid structure of neurons (hardware-implemented) and neurochips with a customized structure of neurons (reprogrammable).

By the possibilities of building neural networks: neural chips with a rigid and variable neural network structure (i.e., neural chips in which the topology of neural networks is rigidly or flexibly implemented).

Processor arrays (systolic processors) are chips that are usually close to conventional RISC processors and unite in their composition a number of processor elements, all the rest of the logic, as a rule, should be implemented on the basis of peripheral circuits.

In a separate class, the so-called neural signal processors should be distinguished, the core of which is a typical signal processor, and the additional logic implemented on the chip ensures the performance of neural network operations (for example, an additional vector processor, etc.).

A generalized classification of neurochips is shown in Figure 1.

Fig.1. Generalized classification of neurochips.

In addition to a wide range of firms and corporations (table 1), research in the field of modern neuroprocessors is carried out by many laboratories and universities, among which may be noted [2]:

For the operational informatization of the scientific community and the creation of a single educational space in the field of neuroinformatics at the Department of Design and Technology of Electronic Equipment Production within the framework of the programs of the Ministry of Education of Russia: Scientific-methodical program "Scientific-methodological support of distant education" and Scientific-technical program "computing equipment , automation, and network integration "work is underway to create an interactive global information-training system in power of neurocomputers and neuroinformatics (http://neurnews.iu4.bmstu.ru, http://cdl.iu4.bmstu.ru).

Neurochips are being developed in many countries around the world. Today [2] there are two basic lines of development of computing systems with mass parallelism (VSMP): VSMP with modified sequential algorithms characteristic of single-processor vonneimanovskih algorithms and VSMP based on fundamentally new saparaplene neural network algorithms for solving various tasks (based on neuromathematics).

Table 1. Neurochip characteristics.

| Name | Manufacturer | Bit rate, bit | Maximum number of synapses * | Maximum number of layers ** | Note |

| MA16 | Siemens | 48 (multipliers and adders) | - | - | 400 mws. |

| NNP (Neural Networks Processor) | Accurate Automation | Nx16 | - | - | MIMD, N is the number of processors. |

| СNAPS-1064 | Adaptive Solutions | sixteen | 128 KB | 64 | |

| 100 NAP Chip | HNC | 32 | 512 KB | four | Plav. Arithmetic 4 processor elements |

| Neuro Matrix NM6403, Tact. frequency 50 MHz. | Module, Russia | 64 (vector processor), 32 RISC core | 4096 pcs. | 24 | Compatible with TMS320C4x ports |

| Neuro Matrix NM6404, Tact. The frequency is 133 MHz. | Module, Russia | 64 (vector processor), 32 RISC core | 4096 pcs. | ~ 48 | Compatible with TMS320C4x ports |

| CLNN 32 CLNN 64 | Bellcore | 32 64 |

496 1024 |

32 neurons | 10 8 switch / s 2 x 10 8 switch / s |

| NC 3001 | Neurigam | sixteen | 4096 pcs. | 32 | |

| ZISC 036 (Zero Instruction Set Computer) | Ibm | 64 bits input vector | - | 36 neurons | Frequency 20 MHz, Vector prototype neurochip |

| ETANN 80170NW | Intel | 64 entries | Two banks of scales 64х80 | 64 neurons in the layer, 3 layers. | Analog |

| MD-1220 | Micro devices | sixteen | 64 pieces | eight | 8 neurons |

| MT 19003 - Neural Instruction Set Processor | Micro Circuit Engineering (MCE) | 16 digits Multiplier 35 bit adder | - | one | RISC MT with 7 special rooms *** |

| Neuro fuzzu | National semiconductor | - | - | - | |

| NI 1000 | Nestor | 5-16 (one neuron) | - | 1024 prototype 256 dimensional vectors | Vector prototype neurochip |

| NLX420 (NLX 110, 230) | Adaptive Logic | sixteen | 1 MB | sixteen | 16 processor elements |

| OBL Chip | Oxford computer | sixteen | 16 MB | - | |

| L-Neuro 1.0 L-Neuro 2.3 |

Philips | sixteen sixteen |

1536 |

16 neurons 192 (12x16) |

26 MHz 60 MHz |

| RSC (Speech Recognition Chip) - 164 | Sensory circuits | - | - | - | |

| ORC 110xx (Object Recognizer Chip) | Synaptics | - | - | - | |

| Pram-256 Chip | UCLi Ltd. | 8 (one neuron) | - | 256 neurons | 33 MHz. |

| SAND | Datafactory | sixteen | - | four | 200 MCPS |

| ACC | sixteen | - | - | ||

| Hercules | Russia | sixteen | 1 MB | 64 | |

| Neuro Classifier | University of Twenta, DESY | 70 in. neurons | - | 6 (internal) 1 in., 1 out. | 2 x 1010 switch / s |

| ANNA | AT & T | The number of neurons 16-256 | 4096 weights | - | The number of inputs in the neuron is 256-16. |

| WSC (Wafer Scale Integration) | Hitachi | - | 64 connections per neuron | 576 neurons | |

| SASLM2 | Mitsubishi | 2 (one neuron) | - | 4096 (64x64) neurons | 50 MHz |

| TOTEM | Kent (Univer UK), di Trento (Italy) | 16 (one neuron) | - | 64 neurons | 30 MHz |

| Neuron 3120, Neurom 3150 | Echelon (USA) | 8 bits (data bus) | - | - | Availability of parallel, serial and communication ports |

To assess the performance of neurocalculators, the following indicators are used:

Orientation in performing neural network operations causes, on the one hand, an increase in the exchange speeds between memory and parallel arithmetic devices, and on the other hand, a reduction in the weight summation (multiplication and accumulation) time due to the use of a fixed set of register-register commands.

Neurochips: analysis and comparative characteristics.

NeuroMatrix NM6403 Neural Signal Processor (Module [9], Russia).

Fig.2. NeuroMatrix NM6403 structure.

The basis of the NeuroMatrix NM6403 is the NeuroMatrixCore (NMC) processor core, which is a synthesis model of a high-performance DSP processor with the VLIM / SIMD architecture (Verilog language). The core consists of two basic blocks: a 32-bit RISC processor and a 64-bit vector processor, which ensures the performance of vector operations on variable-width data (RF patent N2131145). There are two identical programmable interfaces for working with external memory of various types and two communication ports that are hardware compatible with TMS320C4x DSP ports for the possibility of building multiprocessor systems.

Main characteristics:

RISC core

VECTOR coprocessor

Performance:

from 50 to 50.000+ MMAC (millions of multiplications with accumulation per second);

The base for the neural processor are the calculations of the form: Zi = f (Yi) = f (Ui + e (XjWij), (i = 1, .., M; j =, .., N), where Zi is the output signal i-ro neuron, Xj is the jth input signal of the layer, Ui is the i-ro offset of the neuron, Wij is the weighting factor of the jth input of the 1st neuron, Yi is the sum of weighted inputs of the i-th neuron, f is the activation function, N is the number input signals of the layer, M - the number of neurons in the layer; Operands Zi, Xi, Ui and Wij are presented in an additional parallel code and can be of arbitrary bit depth. The main features of this neuroprocessor are:

Fig.3. Constructive implementation of NeuroMatrix 6403.

Specifications:

Due to its versatility, the neuroprocessor can be used as a basic element for PC neuro-accelerators boards, for creating high-performance neurocomputer parallel computing systems, as well as for hardware support of operations on high-dimensional matrices and in problems of digital signal processing. Used in neuro accelerators of the company Module (Russia) [9].

Fig.4 Constructive implementation of the NeuroMatrixR NM6404

NeuroMatrixR NM6404 [9] is a high-performance DSP-oriented RISC microprocessor. It consists of two main blocks: a 32-bit RISC core and a 64-bit VECTOR coprocessor to support operations on vectors with variable-bit elements. NM6404 is compatible with the previous version of the NM6403. There are two identical programmable interfaces for working with external memory of various types and two communication ports that are hardware compatible with TMS320C4x DSP ports for the possibility of building multiprocessor systems.

Features:

RISC core:

VECTOR coprocessor

Performance:

scalar operations:

vector operations:

The NNP (Neural Networks Processor) processor is built according to the MIMD architecture, that is, it consists of several miniature processors operating in parallel. Each of these processors is a fast 16-bit computer with memory for storing synaptic scales. The processor has only 9 simple commands. Processors on a chip are connected to each other by a local bus. NNP was created for commercial purposes and is available in the market.

The processor package includes software development tools, as well as a library of subroutines with implemented neural network algorithms, such as the Hopfield network, the Cohenen network, and others. The processor is supplied on boards for ISA, VME buses. Performance - 140MCPS for a single-processor system, 1.4GCPS for a 10-processor system.

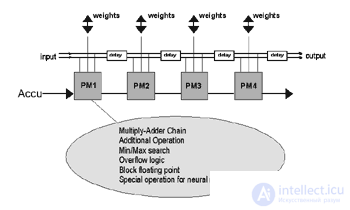

Fig.5. Neurochip MA16 (Siemens).

MA16 is manufactured using CMOS technology (1 micron), consists of 610 thousand transistors and performs up to 400 million multiplication and addition operations per second. It is used as the element base of the Synaps 1 neurocomputer and the Synaps 2 and Synaps 3 neuro accelerators (distributed by the French company Tiga Technologies on the market today).

The MA16 is a programmable cascaded processor for vector and matrix operations. It supports the following operations at the hardware level:

The processor contains four identical processor elements operating in parallel. Input data have an accuracy of 16 bits, the clock frequency of 50 MHz. For matrix multiplication / addition operations, the calculation speed reaches 8_108 operations / s. The software works in UNIX / XWIND environment and is implemented in C ++. The neural network is also described in C ++ or can be entered interactively using a graphical interface such as OSF / Motif, which allows visualizing the configuration of the chip after displaying the network structure on it. Well developed testing and emulation tools. Since 1995, MA16 is a commercially available product.

Fig.6. Functional diagram MA16.

Micro Devices MD1220 digital neurochip contains eight 8-link Nero and 16-bit adders. In-crystal memory stores 16-bit weights. Inputs have one-bit sequential multipliers with a cycle duration of 7.2. ms The average performance is about 9 MCPS.

Neuroprocessor L-Neuro company Philips is one of the first neuroprocessors. Today, its two modifications L-Neuro 1.0 and L-Neuro 2.3 are widely known. The second version has 12 layers, and the first one layer consists of sixteen one-bit, or two eight-bit, or four 4-bit, or two eight-bit processor elements, i.e. has the ability to work multi-bit mode. On-chip 1Kbyte of memory is implemented for storing 1024 8-bit or 512 16-bit scales. The flexible cascaded neurochip structure allows its use in the implementation of various neural network paradigms. When implementing 64 eight-bit processor elements, the average performance is 26 MCPS (32 MCUPS).

Each of the 16 processor elements of the NeuroLogix NLX-420 neurochip contains a 32-bit adder, the logic of parallel execution of 16 multiplications. The average performance is 300 MCPS. There is also the possibility of cascading and multi-bit computing.

Аналоговая СБИС ETANN 80170NX фирмы INTEL содержит 64 входа, 16 внутренних уровней и 64 нейрона (пороговый усилитель с сигмоидной передаточной функцией). Каждый вход соединен с 64 синапсами. Передаточная функция нейрона в СБИС близка к сигмоиде.

Усиление передаточной функции определяет чувствительность нейрона. Низкое значение усиления позволяет интерпретировать выход нейрона как аналоговый, а высокое - как цифровой. Максимальное значение выхода нейрона определяется напряжением Vrefo. Веса ограничены интервалом [-2.5, 2.5]. Скорость прохождения сигнала по одному слою зависит от усиления и примерно равна 1,5 мкс, что и определяет быстродействие. Точность выполнения операций примерно эквивалентна 6 бит, быстродействие - 1,3-109 переключений/с. Обучение выполняется методом Back Propagation с помощью Intel Neural Network Training System (INNTS). Применяемое системное окружение представляет собой специальную версию пакета DynaMind. Обучение выполняется до получения приемлемого уровня ошибки выхода сети, и после достижения удовлетворительной работы веса загружаются в СБИС. Для реальной работы такого обучения недостаточно, так как программа симуляции не может точно смоделировать аналоговую работу СБИС и, например, не отслеживает флуктуации в передаточной функции каждого нейрона. Поэтому следующий этап обучения представляет собой так называемый chip-in-loop (CIL) training, когда после каждого цикла веса записываются в СБИС, и выход сети непосредственно используется в процессе обучения. ТочностьETANN 5-6 разрядов для весов и выходов.

Поскольку ETANN представляет собой аналоговую СБИС, то для ее надежной работы важны стабильные внешние условия. Специально сконструированный для этого модуль обеспечивает низкую пульсацию источника питания 5V < 5 мВ (напряжение питания 5 В) и температурную стабильность при 18°С 8Т < 1°С (потреб***яемая мощность ETANN 5 Вт).

Гибридный нейрочип CLNN32 состоит из 32 нейронов и 496 двунаправленных адаптивных синапсов. CLNN64 содержит только 1024 адаптивных синапсов. В наборе CLNN32/CLNN64 все нейроны взаимосвязаны, так что любая топология сети отображается подбором синапсов. Динамика сети полностью аналоговая, но значения синапсов хранятся/обновляются в цифровом виде с точностью 5 бит. На аппаратном уровне реализовано обучение сети - подбор весов происходит по алгоритму обучения машины Больцмана или Mean Field. Внутри также имеется некоррелированный генератор шума (32 канала), используемый при обучении по методу машины Больцмана. CLNN32 может быть использован независимо или совместно с CLNN64 для построения более сложной архитектуры сети. Производительность достигает 108 переключений/с (при работе с CLNN64 удваивается). Для CLNN32 это означает, что примерно 105 32-бит образцов/с или 32 аналоговых канала (с полосой пропускания 50 кГц) могут быть использованы для быстрого распознавания/обучения. Время распространения для одного слоя нейронов < 1 мкс. "Охлаждение" (по методу Больцмана) или MF обучение требует 10 -20 мкс. По сравнению с ETANN СБИС CLNN32 имеет следующие очевидные преимущества:

Другим примером реализации гибридного нейрочипа является нейрочип ANNA фирмы AT&T. Логика нейрочипа - цифровая, хранение весов - аналоговое (на элементах динамической (конденсаторной) памяти). Чип содержит 4096 весов максимальное число нейронов 256. Точность весов 6 разрядов, для однослойной сети 64x64 производительность достигает 2.1. GCPS.

Аналоговая СБИС NeuroClassifier создана в университете Твенте совместно с DESY. Ее архитектура состоит из входного слоя (70 входов, полоса пропускания до 4 Гбайт/с), шести внутренних слоев и одного выходного нейрона. Точность аналогового умножения 5 бит, время решения всего лишь 20 нс, что позволяет использовать NeuroClassifier в триггере первого уровня. Эквивалентное быстродействие примерно 2_1010 переключений/с.

Компания Datafactory (бывшая INCO) выпустила на рынок SAND/1 (Simple Applicable Neural Device). SAND/1 представляет собой каскадно соединенные систолические процессоры оптимизированные для быстрого решения задач в нейросетевом базисе. Производительность одного процессора составляет 200 MCPS (миллионов связей в секунду). Процессор имеет четыре 16-и битных потока и 40 битный сумматор. SAND/1 был разработан Исследовательским центром в Карлсруе и Институтом микроэлектроники Штутгарта.

Этот нейрочип фирмы Inova SIMD архитектуры относится также, как и предыдущий, к классу систолических нейропроцессоров. Он содержит 80 процессорных элементов, из которых 64 образуют основную матрицу, а 16 являются резервом, 4 Кбайта памяти весов и 32 регистра общего назначения. Арифметический модуль процессора имеет девять параллельных 16 разрядных умножителя и один 32 разрядный сумматор.

Другой систолический нейрочип 100 NAP фирмы Hecht-Nielson Computer содержит 4 32 разрядных процессорных элемента с плавающей точкой. Средняя производительность около 150 MFLOPS, адресуемое адресное пространство внекристалльной памяти 512 Кбайт.

Нейрочип MT19003 фирмы Micro Circuit Engineering, также относится к классу систолических нейропроцессоров. Основой архитектуры является RISC ядро с семью специальными ком***ами, 16 разрядный векторный умножитель и 32 разрядный сумматор, внутрикристалльная память для хранения весов отсутствует. Точность входов и весов 13 разрядов. Средняя производительность 50 MCPS.

Нейропроцессор NEURON ориентирован на создание кластерно-параллельных вычислительных систем. Программно-алгоритмическое обеспечение по управлению кластерной структурой реализовано внутри кристалла. Предложенная архитектура кристалла стала в настоящее время основой стандарта ANSI/EIA 709.1-1999 построения различных АСУ технологическими процессами [2].

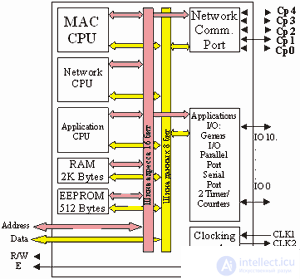

В семействе нейрочипов NEURON выделяют: NEURON 3120 и NEURON 3150. Структурная схема NEURON 3150 приведена на рис7. Кристал содержит 2К динамической памяти для хранения весов и данных, 512 байт (EEPROM), для размещения управляющих программ. Для выполнения специализированных сетевых и управляющих операций в структуре кристалла имеется два спецвычислителя: Applications CPU, Network CPU. Так же следует отметить широкие коммуникационные возможности реализованные на кристалле.

Fig.7. Структурная схема нейрочипа NEURON 3150 фирмы Echelon (США).

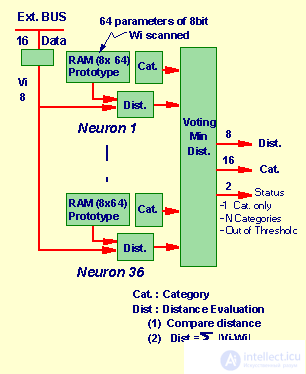

Нейрочип ZISC036 (Zero Instructions Set Computer) фирмы IBM относится к нейрочипам векторно-прототипной архитектуры, т.е. алгоритм обучения стоится на соотношении входного вектора и запомненными прототипными векторами весов входов нейронов. Он содержит 36 нейронов. Ориентирован на решение широкого круга задач, в том числе задач распознавания образов и классификации. Каждый нейрон представляет собой независимый процессор. ZISC способен решать и real-time задачи (рис.8).

Характеристики ZISC036:

Рис.8. Функциональная схема процессора ZISC

Для увеличения производительности фирма IBM разработала ISA и PCI модули параллельно работающих ZISC процессоров.

Рассмотрев основные характеристики элементной базы нейровычислителей, от сигнальных процессоров, ПЛИС до нейрочипов в третьей части обзора мы перейдем к анализу вопросов структурно-функционального построения конкретных нейроускорителей и нейрокомпьютеров на элементной базе , рассмотренной в данном разделе.

Подводя итоги приведем сводные данные по производительности некоторых, наиболее интереснных, нейропроцессоров [1,10-12].

| Наименование нейрочипа | конфигурация | CPS | CPSPW | CPPS | CUPS |

| NLX420 | 32-16, 8 bit mode | 10M | 20K | 640M | - |

| 100 NAP | 4 chips, 2M wts, 16 bit mantissa | 250M | 125 | 256G | 64M |

| WSI (Hitachi) | 576 neuron Hopfield | 138M | 3.7 | 10G | - |

| N64000 (Inova) | 64-64-1, 8 bit mode | 871M | 128K | 56G | 220M |

| MA16 | 1 chip, 25MHz | 400M | 15M | 103G | - |

| ZISC036 | 64 8 bit element inp. Vector | - | - | - | - |

| MT19003 | 4-4-1-, 32 MHz | 32M | 32M | 6.8G | - |

| MD1220 | 8-8 | 9M | 1M | 142M | - |

| NI 1000 | 256 5 bit element inp. Vector | 40 000 vec in sec. | - | - | - |

| L-neuro-1 | 1-chip, 8 bit mode | 26M | 26K | 1.6G | 32M |

| NM6403 | 8 bit mode, 50MHz | 1200M | 150M | 77G | - |

* The table shows average rounded performance figures.

Comments

To leave a comment

Computer circuitry and computer architecture

Terms: Computer circuitry and computer architecture